FRAM Tecnologia e Operação de RAM Ferroelétrica

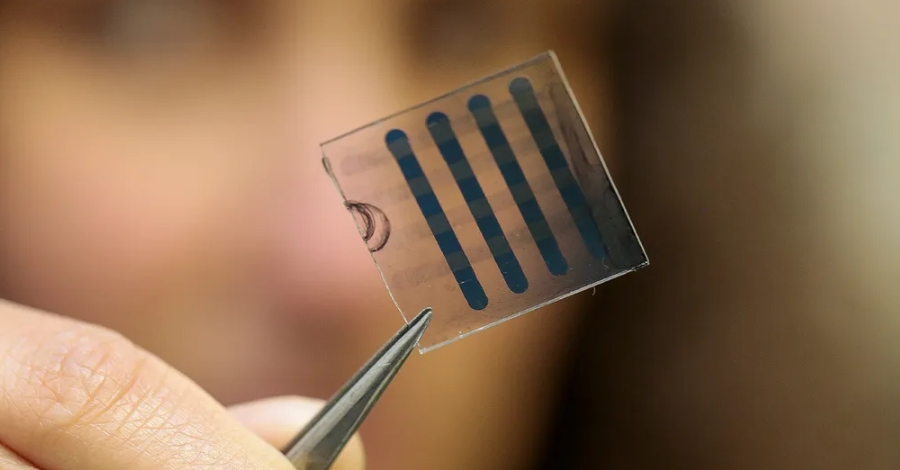

A tecnologia de memória RAM ferroelétrica usa cristais onde o dielétrico tem uma polarização elétrica reversível.

________________________________________

O tutorial sobre memória FRAM inclui:

O que é memória FRAM | Operação e tecnologia FRAM

Tipos de memória:

Tipos e tecnologias de memória | DRAM | EEPROM | Flash | FRAM | MRAM | Memória de mudança de fase | SDRAM | SRAM

_______________________________

A operação e a tecnologia do RAM ferroelétrico são baseadas nas propriedades dos cristais de um dielétrico que possuem uma polarização elétrica reversível.

A tecnologia de memória FRAM não é volátil e combina isso com um número quase ilimitado de ciclos de leitura e gravação. A tecnologia de memória FRAM também oferece um nível muito baixo de consumo de energia, tornando-a uma concorrente para a memória para muitas aplicações.

Embora a tecnologia seja menos densa do que outras tecnologias mais estabelecidas e tenha um custo mais alto, essas questões estão sendo abordadas à medida que o desenvolvimento avança.

O que é o efeito ferroelétrico

Como o nome da memória indica, a tecnologia RAM ferroelétrica depende do efeito ferroelétrico para sua operação. Este efeito tem a capacidade do dielétrico usado mudar sua polarização dependendo da tensão aplicada.

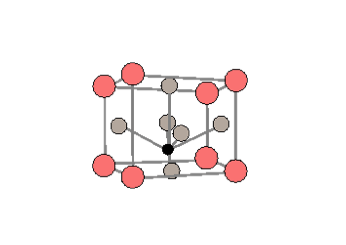

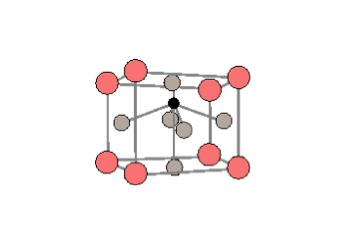

O efeito ferroelétrico é observado em um grupo de materiais conhecidos como perovskitas. Esses materiais têm uma estrutura cristalina com um átomo no centro. Este átomo tem dois estados de baixa energia iguais e estáveis e estes determinam a posição do átomo.

Esta é uma variedade de compostos diferentes que se enquadram nesta categoria. Estes incluem substâncias, incluindo: Titanato Zirconato de Chumbo, etc.

Se um campo for aplicado ao cristal no plano requerido, o átomo se moverá na direção do campo. É a posição do átomo que atua como a determinação do estado do material e, por sua vez, pode ser usada para armazenar dados.

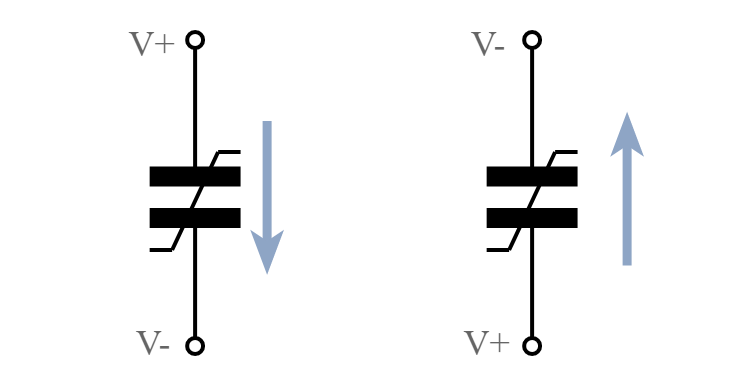

Os dois estados do material ferroelétrico são referidos como ‘polarização ascendente’ quando o átomo está na posição superior e ‘polarização descendente’ quando o átomo está na posição inferior.

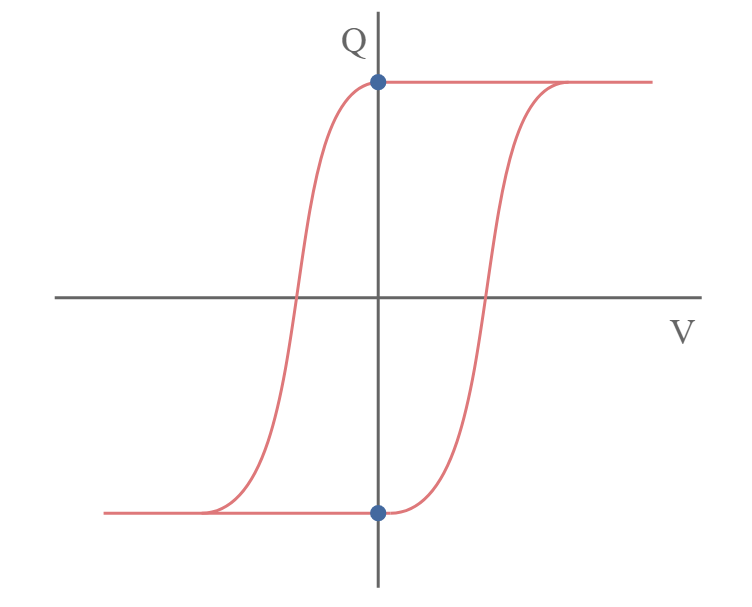

Energia necessária nas transições, e isso significa que há um loop de histerese sobre o qual o material ferroelétrico opera.

Deve-se notar que os cristais ferroelétricos não contêm nenhum material ferroso. Também não são afetados pelo magnetismo. Em vez disso, os materiais ganham seu nome pela semelhança do gráfico de carga plotado em função da tensão com a conhecida curva BH de um material magnético.

Como funciona a memória FRAM?

Pode ser visto que pode haver dois estados diferentes dentro de materiais ferroelétricos. Isso pode ser usado dentro de um capacitor para criar dois estados para uma célula de memória.

O capacitor pode ser polarizado para cima ou para baixo aplicando o campo relevante.

A chave para a operação do FRAM é que a capacitância do capacitor ferroelétrico é variável. Se o capacitor não for comutado quando um campo elétrico for aplicado, ou seja, nenhuma mudança na polarização, então ele se comportará de maneira linear normal. No entanto, se for comutado, uma carga adicional é induzida e isso deve ter resultado de um aumento na capacitância.

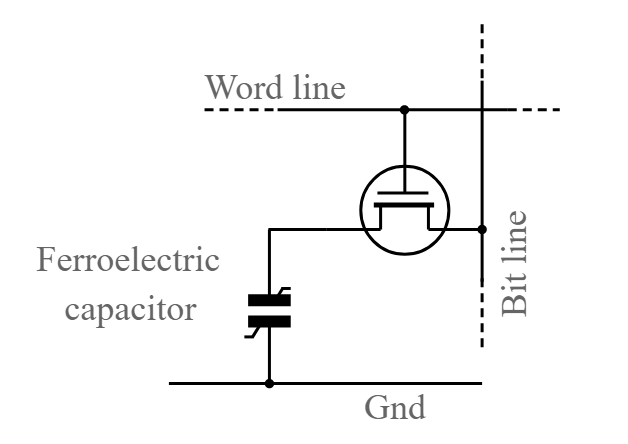

Para permitir que esse efeito seja usado em uma célula de memória, um elemento ativo adicional, um FET, é usado. A célula tem uma linha de palavra e também uma linha de bit para permitir que a célula individual seja acessada.

Ciclo de leitura FRAM

A operação de leitura da memória FRAM requer vários estágios. É muito semelhante ao usado na RAM dinâmica, DRAM. A tensão da linha de bits é simplesmente comparada a uma referência. Essa referência é definida entre os dois níveis, ou seja, acima das tensões não comutadas e abaixo das comutadas. O amplificador de sentido então atua como um comparador amplificando a diferença para dar lógica 1 ou lógica 0.

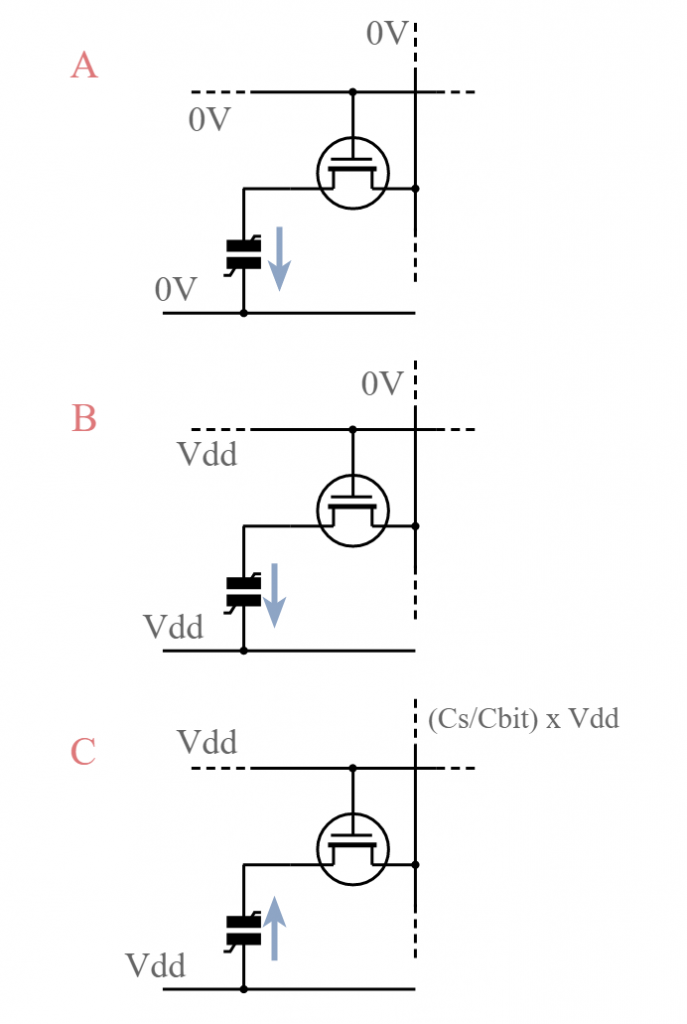

Para observar a sequência mais de perto, a célula estará inicialmente em seu estado inativo, onde a linha de bits é baixa, a linha de placas é baixa e a linha de palavras é baixa, conforme mostrado em ‘A’. Em seguida, progride pela sequência de acesso à memória.

A operação de acesso começa colocando as tensões na Linha de Palavra e na Linha de Placa conforme definido em ‘B’.

Há dois casos que precisam ser considerados. Ao colocar uma tensão no capacitor, ele alternará ou não, dependendo de seu estado.

- Onde o estado do capacitor muda: Essas tensões colocam um campo através do capacitor ferroelétrico que muda conforme mostrado em ‘C’.

Este processo de comutação induz uma carga que é compartilhada com a capacitância da linha de bits representada por Cbit e o capacitor ferroelétrico comutado, Cs. Há também uma pequena capacitância resultante do transistor e outros parasitas de interconexão, mas o efeito geralmente é pequeno.

A tensão resultante na linha de bits é, portanto, proporcional à relação das capacitâncias, Cs : Cbit. Portanto, a tensão na linha de bits é Cs / Cbit x Vdd. - Sem comutação do estado do capacitor: Se o capacitor não comutar, não há carga adicional induzida.

Pode-se observar que os dados dentro da célula podem ser alterados na operação de leitura, ou seja, a leitura de uma célula de memória FRAM é um processo destrutivo. Portanto, requer que a célula seja reescrita se tiver sido alterada.

A operação da memória FRAM é projetada para que a carga induzida no capacitor comutado seja pelo menos duas vezes a carga disponível do capacitor não comutado. Isso significa que a capacitância comutada deve ser pelo menos duas vezes a capacitância não comutada. Segue-se então que a tensão da linha de bits para o caso comutado será pelo menos o dobro do caso não comutado.

Essa tensão pode ser detectada usando amplificadores de detecção semelhantes aos usados em DRAMs.

Também como as DRAMs, as FRAMs têm um tempo de ciclo. Isso significa que o tempo entre acessos aleatórios sucessivos é igual ao tempo de ciclo e não apenas ao tempo de acesso.

Operação de gravação de memória FRAM

A operação FRAM para escrever em endereços de memória usa os mesmos princípios básicos empregados na operação de leitura. O circuito de controle para a memória aplica um campo na direção necessária através do capacitor ferroelétrico para gravar os dados desejados.

Uma vez instalados, os dados permanecerão intactos mesmo quando a energia for removida do chip. Como requer energia para mudar a memória de um estado para outro, a carga não vaza como em outros tipos de memória, incluindo DRAM ou mesmo Flash em um pequeno grau, e permanecerá intacta indefinidamente.

A operação da memória FRAM é relativamente direta. Uma única célula FET é processada junto com um capacitor contendo o dielétrico ferroelétrico. A densidade que essas memórias podem atingir ainda não alcança a de outras tecnologias, mas sua não volatilidade e longa vida significam que é um candidato para muitas aplicações.

____________________________

Retorne ao menu Componentes Eletrônicos

A Raisa distribui equipamentos para soldagem e para teste e medição há mais de 30 anos! Considere explorar algumas das nossa principais categorias através do menu abaixo:

0 Comentários