Operação DRAM: Como a Memória RAM Dinâmica Funciona

RAM dinâmica, a operação DRAM usa um único transistor e capacitor e sua operação é baseada na carga mantida no capacitor.

________________________________________

Tutorial de Memória DRAM Inclui:

Tecnologia de memória DRAM | Como funciona a DRAM | Tipos de DRAM

Tipos de memória:

Tipos e tecnologias de memória | DRAM | EEPROM | Flash | FRAM | MRAM | Memória de mudança de fase | SDRAM | SRAM

_______________________________

A DRAM é uma forma de memória semicondutora, mas opera de maneira ligeiramente diferente de outros formatos.

Para ser capaz de projetar e usar a DRAM, obviamente é sensato ser capaz de compreender a operação da DRAM e sua funcionalidade.

Noções básicas de operação DRAM

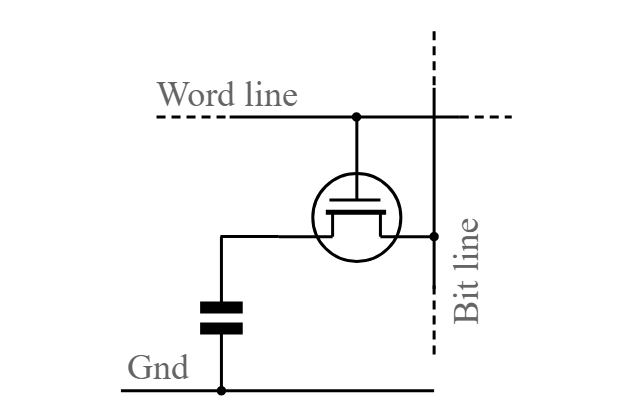

A tecnologia de memória DRAM tem a tecnologia MOS no centro do projeto, fabricação e operação. Observando como funciona uma memória DRAM, pode-se ver que a RAM dinâmica básica ou célula de memória DRAM usa um capacitor para armazenar cada bit de dados e um dispositivo de transferência – um MOSFET – que atua como um interruptor.

O nível de carga no capacitor da célula de memória determina se aquele bit específico é um “1” ou “0” lógico – a presença de carga no capacitor indica um “1” lógico e a ausência de carga indica um “0” lógico.

A célula de memória RAM dinâmica básica tem o formato mostrado abaixo. É muito simples e, como resultado, pode ser densamente compactado em um chip de silício e isso o torna muito barato.

Duas linhas são conectadas a cada célula de RAM dinâmica – a Linha de Palavra (W/L) e a Linha de Bit (B/L) se conectam conforme mostrado para que a célula necessária dentro de uma matriz possa ter dados lidos ou gravados nela.

A célula de memória básica mostrada seria uma entre muitos milhares ou milhões dessas células em um chip de memória completo. As memórias podem ter capacidades de 256 Mbit e mais. Para melhorar os recursos e a velocidade de gravação ou leitura, a memória RAM dinâmica geral pode ser dividida em submatrizes. A presença de múltiplos sub-arrays encurta as linhas de palavra e bit e isso reduz o tempo para acessar as células individuais. Por exemplo, uma RAM dinâmica de 256 Mbit, a DRAM pode ser dividida em 16 matrizes menores de 16 Mbit.

As linhas de palavras controlam as portas das linhas de transferência, enquanto os bines de bits são conectados ao canal FET e, por fim, aos amplificadores de detecção.

Existem duas maneiras pelas quais as linhas de bits podem ser organizadas:

- Linhas de bits dobradas: é possível considerar um par de linhas de bits adjacentes como uma única linha de bits dobrada ao meio com a conexão na dobra quebrada e conectada a um amplificador de sentido compartilhado. Esse formato fornece imunidade adicional a ruídos, mas à custa de ser menos compacto.

- Open Bit Lines: Nesta configuração, as linhas de detecção são colocadas entre dois sub-arrays, conectando assim cada amplificador de detecção a uma linha de bit em cada array. Isso oferece uma solução mais compacta do que as linhas de bits dobradas, mas às custas da imunidade a ruídos.

Operação dinâmica de leitura/gravação de RAM

Uma das questões críticas dentro da RAM dinâmica é garantir que as funções de leitura e gravação sejam realizadas de forma eficaz. Como as tensões nos capacitores de carga são pequenas, a imunidade a ruído é uma questão fundamental.

Existem várias linhas que são usadas nas operações de leitura e gravação:

- /CAS, o Estroboscópio do Endereço da Coluna: Esta linha seleciona a coluna a ser endereçada. As entradas de endereço são capturadas na borda descendente de /CAS. Ele permite que uma coluna seja selecionada da linha aberta para operações de leitura ou gravação.

- /OE, habilitação de saída: O sinal /OE é normalmente usado ao controlar vários chips de memória em paralelo. Ele controla a saída para os pinos de E/S de dados. Os pinos de dados são controlados pelo chip DRAM se /RAS e /CAS forem baixos, /WE for alto e /OE for baixo. Em muitas aplicações, /OE pode ser permanentemente conectado baixo, ou seja, a saída sempre habilitada se não for necessária, por exemplo, se os chips não estiverem conectados em paralelo.

- /RAS, o Strobe do Endereço de Linha: Como o nome indica, a linha /RAS pisca a linha a ser endereçada. As entradas de endereço são capturadas na borda descendente da linha /RAS. A linha é mantida aberta enquanto /RAS permanece baixo.

- /WE, Write Enable: Este sinal determina se uma determinada borda descendente de /CAS é uma leitura ou gravação. Baixo habilita a ação de gravação, enquanto alto habilita uma ação de leitura. Se baixo (escrever), as entradas de dados também são capturadas na borda descendente de /CAS.

Operação de atualização de RAM dinâmica

Um dos problemas com esse arranjo é que os capacitores não mantêm sua carga indefinidamente, pois há algum vazamento no capacitor. Não seria aceitável que a memória perdesse seus dados e, para superar esse problema, os dados são atualizados periodicamente. Os dados são detectados e gravados e isso garante que qualquer vazamento seja superado e os dados sejam restabelecidos.

Um dos elementos-chave da memória DRAM é o fato de que os dados são atualizados periodicamente para superar o fato de que a carga no capacitor de armazenamento vaza e os dados desaparecem após um curto período de tempo. Normalmente, os fabricantes especificam que cada linha deve ser atualizada a cada 64 ms. Este intervalo de tempo está de acordo com os padrões JEDEC para períodos dinâmicos de atualização de RAM.

Há várias maneiras pelas quais a atividade de atualização pode ser realizada. Alguns sistemas de processador atualizam todas as linhas juntas uma vez a cada 64 ms. Outros sistemas atualizam uma linha por vez, mas isso tem a desvantagem de que para grandes memórias a taxa de atualização se torna muito rápida. Alguns outros sistemas (especialmente sistemas de tempo real onde a velocidade é essencial) adotam uma abordagem pela qual uma parte da memória do semicondutor por vez é baseada em um temporizador externo que governa a operação do restante do sistema. Desta forma, não interfere com o funcionamento do sistema.

Qualquer que seja o método usado, é necessário que um contador seja capaz de rastrear a próxima linha na memória DRAM a ser atualizada. Alguns chips DRAM incluem um contador, caso contrário, é necessário incluir um contador adicional para esse fim.

Pode parecer que o circuito de atualização necessário para a memória DRAM complicaria demais o circuito geral da memória, tornando-o mais caro. No entanto, descobriu-se que DRAM, o circuito adicional, não é uma grande preocupação se puder ser integrado ao próprio chip de memória. Verificou-se também que a memória DRAM é muito mais barata e tem uma capacidade muito maior do que o outro concorrente principal que pode ser Static RAM (SRAM).

tamanho DRAM

À medida que o tamanho das memórias aumenta, a questão da relação sinal-ruído torna-se muito importante. À primeira vista, isso pode não parecer um grande problema, mas pode dar origem a problemas de corrupção de dados.

A relação sinal/ruído depende da relação da capacitância do capacitor de armazenamento dentro da memória DRAM para a capacitância da linha Word ou Bit na qual a carga é descarregada quando a célula é acessada. À medida que a densidade de bits por chip aumenta, a proporção é degradada, pois a área da célula diminui à medida que mais células são adicionadas à linha de bits. É por esta razão que é importante armazenar uma voltagem tão alta no capacitor da célula, e também aumentar a capacitância do capacitor de armazenamento DRAM para uma determinada área, tanto quanto possível.

Esta é uma consideração muito importante porque detectar a pequena carga no capacitor da célula de memória é uma das áreas mais desafiadoras do projeto do chip de memória DRAM. Como resultado disso, alguns projetos de circuitos elaborados foram incorporados aos chips de memória DRAM.

Os chips de memória DRAM são amplamente utilizados e a tecnologia está muito bem estabelecida. Tornou-se muito confiável e chips de memória DRAM e placas plug-in estão disponíveis para expandir a memória de computadores e muitos outros dispositivos. Embora a DRAM tenha suas desvantagens, ela ainda é amplamente utilizada porque oferece muitas vantagens em termos de tamanho de custo e velocidade satisfatória – não é a mais rápida, mas ainda mais rápida que alguns tipos de memória.

____________________________

Retorne ao menu Componentes Eletrônicos

A Raisa distribui equipamentos para soldagem e para teste e medição há mais de 30 anos! Considere explorar algumas das nossa principais categorias através do menu abaixo:

0 Comentários